◈ 시스템의 안정적인 동작을 위해 Power Integrity 분석은 필수적인 설계 과정이 되었습니다.

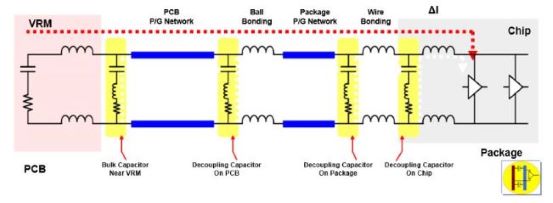

◈ 아래 그림과 같이 VRM 에서 Chip 까지 깨끗한 전원 공급을 위해 진행 되는 모든 과정 이라고 생각 하시면 됩니다.

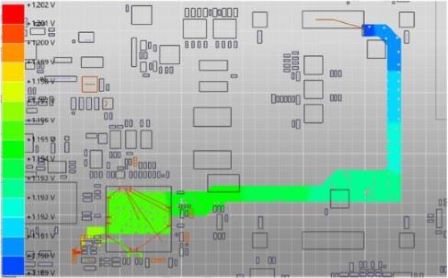

1. IR-Drop

▶ Power source(VRM1, LDO2)에서 Chip 까지의 voltage drop 최소화 해야 합니다.

▶Chip에서 허용하는 오차 안에 들어올 수 있게 design guide 제시합니다.

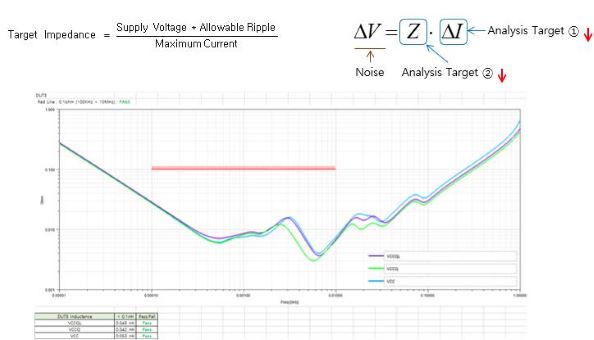

2. Power/Ground Impedance

▶ Chip이 switching 할> 때의 noise 최소화 해야 합니다.

▶ Noise를 줄이고자 하는 power의 허용 오차 및 소모전류를 datasheet에서 확인 후, target impedance를 계산 합니다.

▶ Chip 내 target power의 |Z11|을 target impedance 아래로 낮출 수 있게 design guide를 제시합니다.

Hyperlynx SI / PI

Hyperlynx SI / PI  HFSS / SIwave / Designer

HFSS / SIwave / Designer